Wyzwalacz RS Zasada działania wyzwalacza RS. Schemat

RS-trigger jest prostą maszyną sterującą, zwykle realizowaną w postaci cyfrowego obwodu elektronicznego, należącego do klasy układów sekwencyjnych. Jak wiadomo, w obwodach cyfrowych urządzenia funkcjonalne typu sekwencyjnego obejmują rejestry, liczniki, generatory liczb i automaty kontrolne, w tym wyzwalacze różnego rodzaju.

Umieść wyzwalacze w obwodach cyfrowych

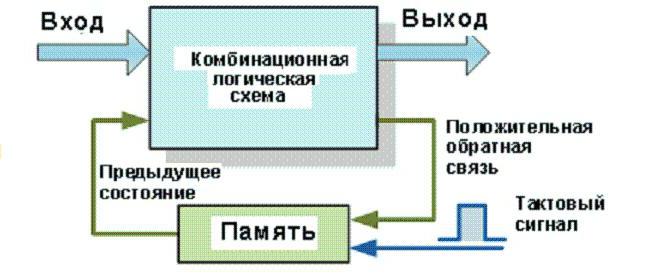

W przeciwieństwie do kombinacyjnych układów logicznych, które zmieniają stan w zależności od rzeczywistych sygnałów zastosowanych do ich wejść w określonym czasie, logika sekwencyjna ma pewną postać wbudowanej wbudowanej "pamięci", dzięki czemu mogą one brać pod uwagę zarówno poprzedni, jak i rzeczywisty stan ich wejść i wychodzi. Ogólny schemat blokowy urządzenia sekwencyjnego pokazano poniżej.

RS-trigger jako cyfrowy automat sterujący zawiera rzeczywistą pamięć i kombinacyjny obwód sterowania na typowych elementach lingwistycznych, które implementują jego algorytm logiki wejściowej. Jeśli uznamy ten obwód za zastosowany do najprostszych obwodów spustowych, to nie mają one uporządkowanej pamięci w postaci jakiegoś wyspecjalizowanego mikroukładu lub węzła obwodu. Pamięć wyzwalacza istnieje na poziomie funkcji, tak jak osadzona w algorytmie jej kombinacyjnego schematu sterowania. Przejawem tej "pamięci" jest tak zwana bistabilność wyzwalacza, którego wyjścia mogą znajdować się w jednym z dwóch podstawowych stanów: jednostki logicznej (zwanej dalej - 1) lub logicznej zero (dalej - 0). Spust zapamiętuje stałe wartości swoich wyjść ("przyciąga" je) i zapisuje, aż do następnej zmiany w swoich sygnałach wejściowych.

Klasyfikacja

Jeżeli standardowe elementy logiki są blokami układów kombinacyjnych, bistabilne obwody, w tym przerzutnik RS, są głównymi składnikami budowania sekwencyjnych urządzeń logicznych, takich jak rejestry do przechowywania danych, rejestry przesuwne, urządzenia pamięciowe lub liczniki. W każdym przypadku rozważane wyzwalacze (oczywiście, jak wszystkie sekwencyjne obwody) mogą być wykonane z następujących podstawowych typów:

1. Asynchroniczny wyzwalacz RS - obwód, który zmienia stan natychmiast po zmianie sygnału wejściowego. Dla danego rodzaju urządzeń są to sygnały na wejściach informacji R (reset) i S (instalacja). Zgodnie z ustaloną praktyką odpowiednie wejścia są nazywane tymi samymi, co sygnały na nich.

2. Synchroniczny wyzwalacz RS, sterowany statycznie , którego praca jest zsynchronizowana z poziomem określonego sygnału zegarowego.

3. Spust według zastrzeżenia 2 z dynamicznym sterowaniem , który jest zsynchronizowany z momentami pojawienia się frontów (lub rozpadów) sygnału zegarowego.

Tak więc, jeśli zmiany stanu wyjść następują tylko w obecności sygnału zegarowego, który jest podawany do osobnego wejścia C zegara, wówczas wyzwalacz jest synchroniczny. W przeciwnym razie obwód jest uważany za asynchroniczny. Aby utrzymać swój aktualny stan, obwody sekwencyjne wykorzystują sprzężenie zwrotne, to znaczy przenoszą część sygnału wyjściowego na jego wejście.

Wyzwalanie RS w elementach logicznych

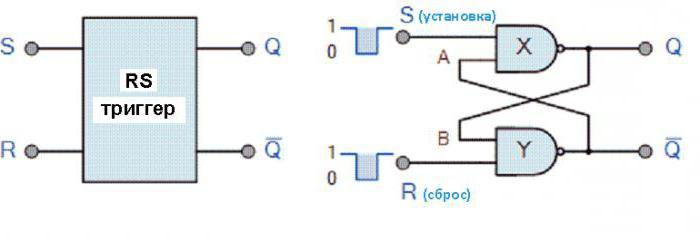

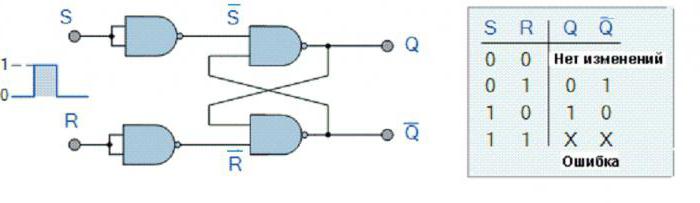

Najprostszym sposobem jest połączenie dwóch elementów logicznych NAND z dwoma wejściami. W takim przypadku sprzężenie zwrotne z wyjścia jednego elementu jest przekazywane do wejścia innego elementu (patrz schemat poniżej).

Z reguły w tym schemacie sygnały wejściowe wykazują odwrotność (z podkreśleniem), chociaż później w analizie pracy wykorzystującej notację bezpośrednich (nieodwróconych) wejść. To bardzo utrudnia zrozumienie logiki wyzwalacza. Dlatego nie wprowadzimy inwersji wejść na etapie rozważania działania obwodu na elementach NAND, ale weźmiemy to pod uwagę w przyszłości, gdy zostanie zmodyfikowany.

Ile wejść i wyjść ma wyzwalacz RS? Z powyższego wykresu widać, że zawiera on wejście S i wejście R, które służą odpowiednio do ustawiania i resetowania obwodu, jak również do bezpośrednich wyjść Q i odwrotnych Q. Ale ten najprostszy wyzwalacz odnosi się do typu asynchronicznego, jego symbol pokazano poniżej.

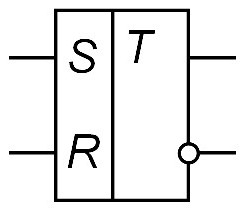

W urządzeniu synchronicznym znajduje się również wejście C dla impulsów zegarowych.

Status "Zainstalowany"

Rozważmy, jak działa RS-flip-flop w tym stanie, podając wartości R = 0 i S = 1. Ponieważ wejście 0 elementu AND-NO Y ma poziom 0, to Q = 1 (logika AND-NO). Z wyjścia Y sygnał Q jest również przesyłany z powrotem do elementu X (wejście "A"). Ponieważ S = A = 1, to Q = 0.

Jeśli R = 1 jest ustawione, a wejście S nadal 1, to na wejściach Y mamy B = 0 i R = 1, a jego wyjście to Q = 1, to znaczy, że się nie zmieniło. Tak więc, jeśli S = 1, wówczas schemat RS wyzwalacza "zatrzaśnie" w stanie "Zainstalowany" Q = 0 i Q = 1, a zmiana sygnału R go nie zmieni.

Status "Resetuj"

W tym drugim stanie ustalonym, Q = 0, i Q = 1, jest on definiowany przez wejścia R = 1 i S = 0. Ponieważ element X ma wejście S = 0, jego wyjście to Q = 1 (logika AND-NOT). Sygnał Q jest przekazywany z powrotem do elementu Y (wejście "B"), a ponieważ R = B = 1, to Q = 0.

Jeśli S staje się równe 1, gdy R = 1, to Q pozostaje równe logowi 0, to znaczy, że nie zmienia się. Tak więc, przy R = 1, obwód wyzwalający jest ponownie "zatrzaśnięty" w stanie "Reset" Q = 0 i Q = 1, zapisany przy dowolnym sygnale S.

Podsumowujemy wyniki w tabeli

Możemy określić stan sygnałów Q i Q, korzystając z poniższej tabeli prawdy:

| Stan | S | R | Q | Q | Opis |

| Instalacja | 1 | 0 | 0 | 1 | Wyjście Q = 1 |

| 1 | 1 | 0 | 1 | bez zmian | |

| Zresetuj | 0 | 1 | 1 | 0 | Wyjście Q = 0 |

| 1 | 1 | 1 | 1 | bez zmian | |

| Nieprawidłowy | 0 | 0 | 1 | 1 | stan błędu |

Można zauważyć, że gdy S = R = 1, to Q i Q mogą być równe 1 lub 0 (ale nie jednocześnie!) W zależności od poziomów wejść S lub R przed wystąpieniem tego stanu wyjść. Zatem w warunkach S = R = 1 stan wyjść Q i Q nie może być zmieniony. Może zmienić się tylko wtedy, gdy zmienisz poziom z 1 na 0 na jednym z wejść.

Wartość S = R = 0 jest niepożądanym lub niedopuszczalnym stanem i należy go unikać. Stan S = R = 0 powoduje, że oba wyjścia Q i Q mają być ustawione na poziomie 1, podczas gdy stan Q powinien zawsze powrócić do Q. Rezultatem jest to, że wyzwalacz traci kontrolę nad Q i Q, a jeśli dwa wejścia przejdą teraz do stanu 1, obwód staje się niestabilny i przełącza się do niezdefiniowanego stanu.

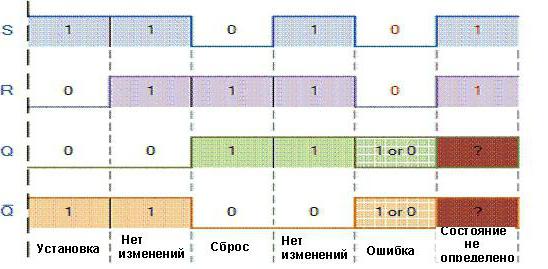

Wykres przełączania wyzwalacza RS

To, co zostało powiedziane w poprzednim rozdziale, zostało zilustrowane poniższym schematem przełączania.

Jak widać, gdy S = R = 0, powstaje nierównowaga (stan niepewności) stanu wyjściowego. Może to prowadzić do przełączania jednego z wyjść szybciej niż inne, w wyniku czego spust przejdzie na jeden lub inny stan, który może nie pokrywać się z wymaganym, a dane zostaną uszkodzone. Ten niestabilny stan nazywa się zwykle metastabilnym.

W związku z tym podobny zatrzask spustowy może zostać przeniesiony do stanu "Zainstalowany" poprzez wypełnienie 0 na jego wejściu S (jeśli jest 1 na wejściu R) i przeniesiony do stanu "Reset" przez zastosowanie 0 do wejścia R (jeśli jest 1 na S-enter). Wyzwalacz wchodzi w niezdefiniowany stan (metastabilny), jeśli poziom 0 jest jednocześnie zastosowany do obu jego wejść.

Przełączanie stanu wyjść następuje z niewielkim opóźnieniem w stosunku do zmiany sygnału na jednym z wejść bez użycia sygnału zegarowego. Dlatego powyższy schemat jest asynchronicznym wyzwalaczem RS.

Zmodyfikuj schemat wyzwalania

Jak widzieliśmy powyżej, podstawowe elementy IS-NOT w rozpatrywanym RS-flip-flopie działają tak, że gdy jest ustawione, Q = 1 i Q = 0, i kiedy jest on resetowany, Q = 0 i Q = 1, chociaż byłoby logiczne mieć Q w pierwszym stanie = 1, aw drugim - Q = 0. W tym przypadku okazuje się również, że zmiana stanów następuje, gdy poziom sygnału spada z 1 na 0.

Tak więc, dla prawidłowego działania obwodu wyzwalającego, jego sygnały wejściowe muszą być odwrócone. Wtedy przełączenie jego stanów nastąpi przy zastosowaniu dodatnich sygnałów wejściowych. Aby to zrobić, dodaj dwa dodatkowe elementy IS-NOT do obwodu, podłączone jako falowniki do wejść S i R, jak pokazano na poniższym rysunku. Tutaj wejścia elementów AND-NOT już reprezentowały odwrotne sygnały wejściowe.

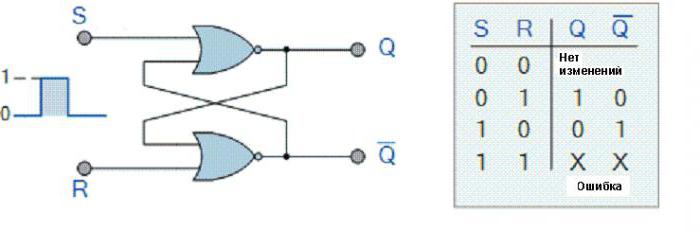

Podobnie jak przy użyciu elementów AND-NOT, można zbudować prosty wyzwalacz RS, używając dwóch elementów OR-NOT połączonych w ten sam sposób. Będzie działać tak samo, jak schemat NAND omówiony powyżej. Jednocześnie aktywny jest wysoki poziom sygnałów na wejściach, a niedopuszczalny stan występuje, gdy poziom logiczny "1" jest zastosowany do obu wejść, jak pokazano w tabeli prawdy na poniższym rysunku.

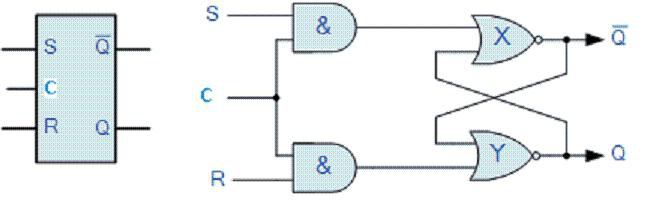

Jak zsynchronizować wyzwalacz

Czasem pożądane jest posiadanie bistabilnego wyzwalacza w sekwencyjnych układach logicznych, który zmienia swój stan, gdy spełnione są określone warunki, niezależnie od stanu wejść S lub R. Taki schemat można utworzyć, łącząc element z dwoma wejściami ORAZ sekwencyjnie z każdym wejściem wyzwalacza. Łącząc dwa wejścia elementów A, otrzymujemy nowe wejście wyzwalacza. Dodanie go oznacza, że wyjścia Q i Q выход zmieniają stan, gdy sygnał na nim jest wysoki, a zatem może on być użyty jako wejście C zegara, jak pokazano na poniższym rysunku.

Kiedy sygnał na wejściu C jest na poziomie 0, wyjścia dwóch elementów I są również na poziomie 0 (logika elementu I), niezależnie od stanu dwóch wejść S i R, a dwa wyjścia Q i Q są "zablokowane" w ostatnim stanie ustalonym. Kiedy sygnał na wejściu C zmienia się na poziom 1, obwód reaguje jako normalny bistabilny wyzwalacz, stając się przezroczystym dla ustawiania i resetowania stanów.

To dodatkowe wejście C można również podłączyć do wyjścia generatora częstotliwości zegara, a następnie utworzyć synchroniczny przerzutnik RS. Tak więc, ten schemat działa jako standardowy bistabilny wyzwalacz "zatrzask", ale wyjścia są aktywowane tylko wtedy, gdy poziom 1 jest doprowadzany do wejścia C, i są wyłączane, gdy pojawia się logiczny poziom zerowy.

Rejestry wyzwalaczy

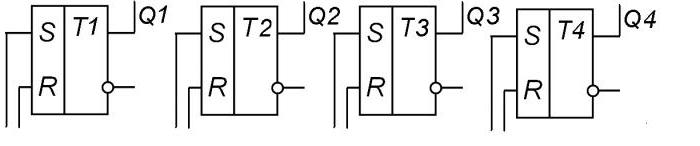

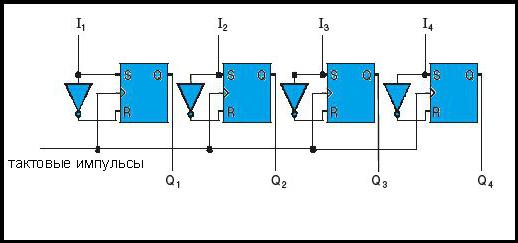

Wyzwalacz RS może przechowywać 1 bit informacji cyfrowej. Jeśli konieczne jest zapisanie kilku bitów, na przykład, binarnego słowa cyfrowego kilku bitów binarnych (w mikrokontrolerach, zwykle 8 lub 16), to wyzwalacze mogą być połączone równolegle, tworząc rejestry. Są to najprostsze urządzenia do tymczasowego przechowywania zestawu binarnych cyfr cyfrowych, w których każdy wyzwalacz przechowuje wartość jednej cyfry (0 lub 1. czyli jeden bit). Tak więc rejestr 4-bitowy pokazany poniżej na przerzutnikach RS zawiera cztery osobne klapki.

Każda liczba binarna z (0000) od 2 do (1111) 2 może być zapisana w tym rejestrze po prostu przez ustawienie lub zresetowanie odpowiedniego wyzwalacza. Załóżmy, że pierwszy wyzwalacz jest ustawiony (Q1 = 1), drugi jest resetowany (Q2 = 0), trzeci również jest resetowany (Q3 = 0), a czwarty jest ustawiony (Q4 = 1). Wtedy liczba binarna zapisana w rejestrze będzie wynosić (1001) 2.

Oprócz rejestrów równoległych przeznaczonych do przechowywania słów cyfrowych, tak zwane rejestry przesuwne są wykonywane na przerzutnikach RS, w których cyfry cyfrowego słowa sukcesywnie wraz z nadejściem każdego impulsu zegara są przesunięte w lewo lub w prawo o jeden bit. Schemat takiego urządzenia na wyzwalaczach synchronicznych pokazano poniżej.

Rejestry takie są używane w obwodach interfejsu szeregowego, gdy słowa cyfrowe pochodzące od kontrolera kontrolnego są przekazywane nieco do linii komunikacyjnej.